Программируемая пользователем вентильная матрица

Программи́руемая по́льзователем ве́нтильная ма́трица (ППВМ, англ. field-programmable gate array, FPGA) — полупроводниковое устройство, которое может быть сконфигурировано производителем или разработчиком после изготовления; наиболее сложная по организации разновидность программируемых логических интегральных схем.

Программируются путём изменения логики работы принципиальной схемы, например, с помощью исходного кода на языке описания аппаратуры (например, Verilog). Могут быть модифицированы практически в любой момент в процессе их использования. Cостоят из конфигурируемых логических блоков, подобных переключателям с множеством входов и одним выходом (логические вентили, gates). В цифровых схемах такие переключатели реализуют базовые двоичные операции AND, NAND, OR, NOR и XOR. Принципиальное отличие ППВМ состоит в том, что и функции блоков, и конфигурация соединений между ними могут меняться с помощью специальных сигналов, посылаемых схеме. В некоторых специализированных интегральных схемах (ASIC) используются логические матрицы, аналогичные ППВМ по строению, однако они конфигурируются один раз в процессе производства, в то время как ППВМ могут постоянно перепрограммироваться и менять топологию соединений в процессе использования. Однако такая гибкость требует существенного увеличения количества транзисторов микросхемы.

История[править | править код]

В ранних ПЛИС программированием можно было изменять только связи между вентилями[1]; в 1985 году сооснователи Xilinx Росс Фримен (англ. Ross Freeman) и Бернард Вандершмит (англ. Bernard V. Vonderschmitt) разработали первую коммерчески успешную ППВМ — XC2064, имеющую программируемые вентили и программируемые соединения между ними (в 2005 году за это изобретение Фримен был занесён в Национальный зал славы изобретателей США). Сама концепция программируемых вентильных матриц, логических вентилей и логических блоков запатентована Дэвидом Пейджем и Луверном Петерсоном в 1985 году[2][3]. В 1990-х годах произошёл резкий скачок интереса к ППВМ, возросла их сложность и объёмы производства: если в первые годы они использовались в основном в области телекоммуникаций и сетей связи, то к концу десятилетия они нашли применение в потребительских товарах, в автомобильной промышленности и других отраслях.

В 1997 году Адриан Томпсон объединил генетические алгоритмы и технологию ППВМ для создания устройства, способного отличать звуковые тоны частотой 1 КГц и 10 КГц. Генетические алгоритмы позволили с помощью вентильной матрицы размером 64×64 на микросхеме фирмы Xilinx создать конфигурацию, необходимую для решения поставленной задачи[4]. В те же годы начали широко применяться для прототипирования специализированных интегральных схем и процессоров общего назначения. В начале 2000-х годов ППВМ начали использоваться для ускорения специфических операций в серверных узлах как в индустрии высокопроизводительных вычислений, так и в машинах баз данных (Netezza). Во второй половине 2010-х годов отмечен всплеск интереса к технологии в связи с эффективностью применения для глубокого обучения (прежде всего за счёт возможности реализации арифметики с пониженной точностью и безрегистровых вычислений — аналога тензорного процессора Google), а у инфраструктурных облачных провайдеров появилась возможность приобрести ППВМ по подписке из публичного облака (Amazon F1, Baidu, Tencent, Huawei).

К 2018 году объём мирового рынка ППВМ составил около $5,7 млрд, крупнейшие производители — Xilinx (51 % рынка), Intel (36 %, за счёт активов Altera), Microchip (17 %), Lattice Semiconductor (9 %)[5].

Архитектура[править | править код]

В ППВМ имеется три типа программируемых элементов:

- нескоммутированные программируемые логические блоки (ПЛБ);

- блоки ввода-вывода (БВВ);

- внутренние связи.

ПЛБ являются функциональными элементами для построения логики пользователя. БВВ обеспечивают связь между контактами корпуса и внутренними сигнальными линиями. Программируемые ресурсы внутренних связей обеспечивают управление путями соединения входов и выходов ПЛБ и блоков ввода-вывода (БВВ) на соответствующие сети[6]. Все каналы трассировки имеют одинаковую ширину (одинаковое количество проводников). Большинство блоков ввода-вывода (БВВ) вписываются либо в одну строку (по высоте), либо в один столбец (по ширине) массива вентилей.

Логический блок (ПЛБ) классической ППВМ состоит из таблицы истинности (англ. lookup table, LUT) на несколько входов и один триггер (в ранних реализациях использовалось 4 входа, впоследствии — большее число входов, что позволило задействовать меньшее число логических блоков для типичных приложений[7]).

Логический блок (ПЛБ) имеет таблицу истинности на четыре входа и вход синхронизации (clock). Выход блока только один — регистровая или нерегистровая выходная таблица истинности. Поскольку сигналы синхронизации в коммерческих ППВМ (а часто и другие сигналы, распараллеливающиеся на большое количество входов — high-fanout signals) трассируются особым образом специальными трассировочными цепями, управление этими сигналами делается отдельно.

Для приведённого примера архитектуры расположение контактов логического блока показано ниже.

Входы расположены на отдельных сторонах логического блока; выходной контакт может трассироваться в двух каналах: либо справа от блока, либо снизу. Выходные контакты каждого логического блока могут соединяться с трассировочными сегментами в смежных каналах. Аналогично, контактная площадка блока ввода-вывода (pad) может соединяться с трассировочным элементом в любом смежном канале. Например, верхняя контактная площадка чипа может соединяться с любым из W проводников (где W — ширина канала) в горизонтальном канале, расположенном непосредственно под ним.

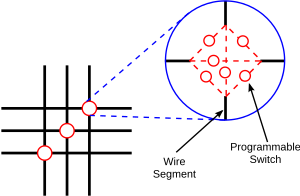

Как правило, трассировка ППВМ несегментирована, то есть каждый сегмент проводника соединяет только один логический блок с переключательным блоком. Из-за огибания программируемых переключателей в переключательном блоке трассировка получается более длинной. Для увеличения скорости внутрисистемных соединений, в некоторых архитектурах ППВМ между логическими блоками используются более длинные трассировочные соединения.

В месте пересечения вертикальных и горизонтальных каналов создаются переключательные блоки. При такой архитектуре для каждого проводника, входящего в переключательный блок, существуют три программируемых переключателя, которые позволяют ему подключаться к трём другим проводникам в смежных сегментах канала. Модель или топология выключателей, используемая в этой архитектуре, является планарной или доменной топологией переключательных блоков. В этой топологии проводник трассы номер 1 подключается только к проводнику трассы номер 1 в смежных каналах, проводник трассы номер 2 подключается только к проводникам трассы номер 2 и так далее.

Современные семейства ППВМ расширяют перечисленные выше возможности и обладают встроенными функциями высокого уровня, благодаря наличию которых удаётся уменьшить площадь кристалла и ускорить выполнение типовых подзадач в сравнении с реализацией на основе примитивов. Примерами таких функций являются мультиплексоры, блоки цифровой обработки сигналов, встроенные процессоры, быстрая логика ввода-вывода и встроенная память.

ППВМ также широко применяются для систем проверки пригодности, в том числе в докремниевой и послекремниевой проверке пригодности, а также при разработке программ для встраиваемых систем. Это позволяет компаниям-производителям интегральных схем проверять работоспособность своих устройств до изготовления их на заводе, сокращая время выхода изделия на рынок.

Примечания[править | править код]

- ↑ History of FPGAs (англ.)

- ↑ Google Patent Search, «Re-programmable PLA».

- ↑ Google Patent Search, «Dynamic data re-programmable PLA».

- ↑ On the Origin of Circuits. Дата обращения: 4 мая 2012. Архивировано 27 апреля 2012 года.

- ↑ Doug Black. Xilinx Says Its New FPGA is World’s Largest. Enterprise AI (21 августа 2019). Дата обращения: 3 августа 2020. Архивировано 4 ноября 2020 года.

- ↑ Архитектура FPGA Архивная копия от 11 мая 2018 на Wayback Machine (англ.)

- ↑ Achieving Higher System Performance with the Virtex-5 Family of FPGA, WP245 (v1.1.1) July 7, 2006 Архивировано 27 сентября 2007 года. xilinx.com (англ.)