Триггер: различия между версиями

| [непроверенная версия] | [непроверенная версия] |

→Т-триггер асинхронный: дополнение |

|||

| Строка 258: | Строка 258: | ||

=== Т-триггер асинхронный === |

=== Т-триггер асинхронный === |

||

Асинхронный Т-триггер не имеет входа разрешения переключения Т. |

Асинхронный Т-триггер не имеет входа разрешения переключения Т. |

||

[[File:Ttrigasinhr.jpg|right|thumb|300px| |

[[File:Ttrigasinhr.jpg|right|thumb|300px|Логическая схема асинхронного двухступенчатого Т-триггера на двух парафазных D-триггерах и инверторе]] |

||

[[Файл:T flip-flop.gif|справа|мини|170px|Работа схемы асинхронного двухступенчатого T-триггера с парафазным входом на двух парафазных D-триггерах на восьми [[Логический вентиль|логических вентилях]] '''2И-НЕ'''. Слева — входы, справа — выходы. Синий цвет соответствует 0, красный — 1]] |

[[Файл:T flip-flop.gif|справа|мини|170px|Работа схемы асинхронного двухступенчатого T-триггера с парафазным входом на двух парафазных D-триггерах на восьми [[Логический вентиль|логических вентилях]] '''2И-НЕ'''. Слева — входы, справа — выходы. Синий цвет соответствует 0, красный — 1]] |

||

Версия от 15:16, 26 октября 2010

Триггер (амер. flip-flop) (триггерная система) — класс электронных устройств, обладающих способностью длительно находиться в одном из двух или более устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко распознаётся по значению выходного напряжения. По характеру действия триггеры относятся к импульсным устройствам — их активные элементы (транзисторы, лампы) работают в ключевом режиме, а смена состояний длится очень короткое время.

Отличительной особенностью триггера как функционального устройства является свойство запоминания двоичной информации. Под памятью триггера подразумевают способность оставаться в одном из двух состояний и после прекращения действия переключающего сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер хранит (помнит) один разряд числа, записанного в двоичном коде.

При изготовлении триггеров применяются преимущественно полупроводниковые приборы (обычно биполярные и полевые транзисторы), в прошлом — электромагнитные реле, электронные лампы. В настоящее время логические схемы, в том числе с использованием триггеров, создают в интегрированных средах разработки под различные программируемые логические интегральные схемы (ПЛИС). Используются в основном в вычислительной технике для организации компонентов вычислительных систем: регистров, счётчиков, процессоров, ОЗУ.

История

Разрывные характеристики электронных ламп, на которых основано действие триггеров, впервые под названием «катодное реле» были описаны М. А. Бонч-Бруевичем в 1918 г.[1] Практическая схема триггера была опубликована 5 августа 1920 года У. Г. Икклзом?! и Ф. У. Джорданом в патенте Великобритании № 148582 заявленном 21 июня 1918 г.[2] и в статье «Переключающее реле, использующее трёхэлектродные вакуумные лампы»[3] от 19 сентября 1919 года.

Определения

Триггер (бистабильный мультивибратор[4]) — это цифровой автомат, имеющий несколько входов и 2 выхода.

Триггер — это устройство последовательного типа с двумя устойчивыми состояниями равновесия, предназначенное для записи и хранения информации. Под действием входных сигналов триггер может переключаться из одного устойчивого состояния в другое. При этом напряжение на его выходе скачкообразно изменяется.

Триггерами называют[5] такие логические устройства, выходные сигналы которых определяются не только сигналами на входах, но и предысторией их работы, то есть состоянием элементов памяти.

Триггер — один из базовых (основных) элементов цифровой техники[6]. Некоторые исследователи[7] включают триггер в 100 великих изобретений.

Триггер не является логическим элементом первого уровня, а сам состоит из логических элементов первого уровня — инверторов или логических вентилей. По отношению к логическим элементам первого уровня триггер является логическим устройством второго уровня.

Триггер — элементарная ячейка оперативной памяти.

Триггер — простейшее устройство, выполняющее логическую функцию с обратной связью, то есть простейшее устройство кибернетики.

Триггер — это запоминающий элемент с двумя (или более) устойчивыми состояниями, изменение которых происходит под действием входных сигналов и предназначен для хранения одной единицы информации (бита, трита, ...).

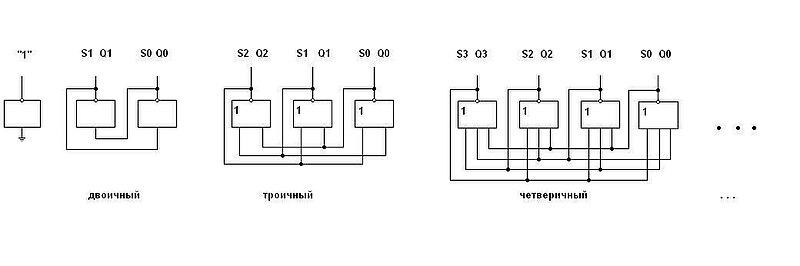

N-ичный триггер — устройство (элементарная переключаемая ячейка памяти, переключатель с N устойчивыми положениями), которое имеет N устойчивых состояний и возможность переключения из любого состояния в любое другое состояние.

Классификация

Триггеры подразделяются на две большие группы — динамические и статические. Названы они так по способу представления выходной информации.

Динамический триггер представляет собой систему, одно из состояний которой (единичное) характеризуется наличием на выходе непрерывной последовательности импульсов определённой частоты, а другое — отсутствием выходных импульсов (нулевое). Смена состояний производится внешними импульсами (рис. 3). Динамические триггеры в настоящее время используются редко.

К статическим триггерам относят устройства, каждое состояние которых характеризуется неизменными уровнями выходного напряжения (выходными потенциалами): высоким — близким к напряжению питания и низким — около нуля. Статические триггеры по способу представления выходной информации часто называют потенциальными.

Статические (потенциальные) триггеры, в свою очередь, подразделяются на две неравные по практическому значению группы — симметричные и несимметричные триггеры. Оба класса реализуются на двухкаскадном усилителе с положительной обратной связью, а названием своим они обязаны способам организации внутренних электрических связей между элементами схемы.

Симметричные триггеры отличает симметрия схемы и по структуре, и по параметрам элементов обоих плеч. Для несимметричных триггеров характерна неидентичность параметров элементов отдельных каскадов, а также и связей между ними.

Симметричные статические триггеры составляют основную массу триггеров, используемых в современной радиоэлектронной аппаратуре. Схемы симметричных триггеров в простейшей реализации (2х2ИЛИНЕ) показаны на рис. 4.

Основной и наиболее общий классификационный признак — функциональный — позволяет систематизировать статические симметричные триггеры по способу организации логических связей между входами и выходами триггера в определённые дискретные моменты времени до и после появления входных сигналов. По этой классификации триггеры характеризуются числом логических входов и их функциональным назначением (рис. 5).

Вторая классификационная схема, независимая от функциональной, характеризует триггеры по способу ввода информации и оценивает их по времени обновления выходной информации относительно момента смены информации на входах (рис. 6).

Каждая из систем классификации характеризует триггеры по разным показателям и поэтому дополняет одна другую. К примеру, триггеры RS-типа могут быть в синхронном и асинхронном исполнении.

Асинхронный триггер изменяет своё состояние непосредственно в момент появления соответствующего информационного сигнала(ов), с некоторой задержкой равной сумме задержек на элементах составляющих данный триггер.

Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации С (от англ. clock). Этот вход также обозначают термином «такт». Такие информационные сигналы называют синхронными. Синхронные триггеры в свою очередь подразделяют на триггеры со статическим (статические) и динамическим (динамические) управлением по входу синхронизации С.

Одноступенчатые триггеры состоят из одной ступени представляющей собой элемент памяти и схему управления, делятся на триггеры со статическим управлением и триггеры с динамическим управлением.

Триггеры со статическим управлением воспринимают информационные сигналы при подаче на вход С логической единицы (прямой вход) или логического нуля (инверсный вход).

Триггеры с динамическим управлением воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход). Также встречается название «триггер управляемый фронтом».

Двухступенчатые триггеры бывают, как правило, со статическим управлением. При одном уровне сигнала на входе С информация, в соответствии с логикой работы триггера, записывается в первую ступень (вторая ступень заблокирована для записи). При другом уровне этого сигнала происходит копирование состояния первой ступени во вторую (первая ступень заблокирована для записи), выходной сигнал появляется в этот момент времени с задержкой равной задержке срабатывания ступени. Обычно двухступенчатые триггеры применяются в схемах, где логические функции входов триггера зависят от его выходов, во избежание временны́х гонок. Двухступенчатые триггеры с динамическим управлением встречаются крайне редко. Двухступенчатый триггер обозначают ТТ.

Триггеры со сложной логикой бывают также одно- и двухступенчатые. В этих триггерах наряду с синхронными сигналами присутствуют и асинхронные. Такой триггер изображён на рис. 1, верхний (S) и нижний (R) входные сигналы являются асинхронными.

Триггерные схемы классифицируют также по следующим признакам:

- числу целочисленных устойчивых состояний (основанию системы счисления) (обычно устойчивых состояний два, реже — больше, см. двоичный триггер, троичный триггер, четверичный триггер[8], …, десятичный триггер, …, n-ичный триггер, …);

- числу уровней — два уровня (высокий, низкий) в двухуровневых элементах, три уровня (положительный, ноль, отрицательный) в трёхуровневых элементах[9], …, N-уровней в N-уровневых элементах, … ;

- по способу реакции на помехи — прозрачные и непрозрачные. Непрозрачные, в свою очередь, делятся на проницаемые и непроницаемые.

- по составу логических элементов (триггеры на элементах И-НЕ, ИЛИ-НЕ и др.).

Базовые понятия

Все разновидности триггеров представляют собой элементарный автомат, включающий собственно элемент памяти (ЭП) и комбинационную схему (КС), которая может называться схемой управления или входной логикой (рис. 7).

В графе триггера каждая вершина графа соединена со всеми другими вершинами, при этом переходы от вершины к вершине возможны в обе стороны (двухсторонние). Граф двоичного триггера — две точки соединённые отрезком прямой линии, троичного триггера — треугольник, четверичного триггера — квадрат с диагоналями, пятеричного триггера — пятиугольник с пентаграммой и т. д. При N=1 граф триггера вырождается в одну точку, в математике ему соответствует унарная единица или унарный ноль, а в электронике — монтажная «1» или монтажный «0», то есть простейшее ПЗУ. Устойчивые состояния имеют на графе триггера дополнительную петлю, которая обозначает, что при снятии управляющих сигналов триггер остаётся в установленном состоянии.

Состояние триггера определяется сигналами на прямом и инверсном выходах. При положительном кодировании (позитивная логика) высокий уровень напряжения на прямом выходе отображает значение лог. 1 (состояние = 1), а низкий уровень — значение лог. 0 (состояние = 0). При отрицательном кодировании (негативная логика) высокому уровню (напряжению) соответствует логическое значение "0", а низкому уровню (напряжению) соответствует логическое значение "1".

Изменение состояния триггера (его переключение или запись) обеспечивается внешними сигналами и сигналами обратной связи, поступающими с выходов триггера на входы схемы управления (комбинационной схемы или входной логики). Обычно внешние сигналы, как и входы триггера, обозначают латинскими буквами R, S, T, C, D, V и др. В простейших схемах триггеров отдельная схема управления (КС) может отсутствовать. Поскольку функциональные свойства триггеров определяются их входной логикой, то названия основных входов переносятся на всю схему триггера.

Входы триггеров разделяются на информационные (R, S, T и др.) и управляющие (С, V). Информационные входы предназначены для приема сигналов запоминаемой информации. Названия входных сигналов отождествляют с названиями входов триггера. Управляющие входы служат для управления записью информации. В триггерах может быть два вида управляющих сигналов:

- синхронизирующий (тактовый) сигнал С, поступающий на С-вход (тактовый вход);

- разрешающий сигнал V, поступающий на V-вход.

На V-входы триггера поступают сигналы, которые разрешают (V=1) или запрещают (V=0) запись информации. В синхронных триггерах с V-входом запись информации возможна при совпадении сигналов на информационном С и V-входах.

Каждый тип триггера имеет собственную таблицу работы (таблицу истинности). Выходное состояние триггера обычно обозначают буквой Q. Индекс возле буквы означает состояние до подачи сигнала (t) или после подачи сигнала (t+1). В триггерах с парафазным (двухфазным) выходом имеется второй (инверсный) выход, который обозначают как Q, /Q или Q'.

Кроме табличного определения работы триггера существует формульное задание функции триггера в секвенциальной логике. Например, функцию RS-триггера в секвенциальной логике представляет формула . Аналитическая запись SR-триггера выглядит так: .

Типы триггеров

Логические схемы триггеров не зависят от физического исполнения логических элементов (РТЛ, ДТЛ, ТТЛ, КМОП, ЭСЛ и др.) и являются общими для всех видов физического исполнения логических элементов.

RS-триггеры

RS-триггер асинхронный

| S | R | Q(t) | Q(t) | Q(t+1) | Q(t+1) |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 |

RS-триггер[10][11], или SR-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы. Граф RS-триггера показан на рис. 9.

При подаче единицы на вход S (от англ. Set — установить) выходное состояние становится равным логической единице. А при подаче единицы на вход R (от англ. Reset — сбросить) выходное состояние становится равным логическому нулю. Состояние, при котором на оба входа R и S одновременно поданы логические единицы, в некоторых случаях является запрещённым, при такой комбинации RS-триггер переходит в третье состояние QQ=00. Одновременное снятие двух «1» практически невозможно. При снятии одной из «1» RS-триггер переходит в состояние, определяемое оставшейся «1». Таким образом RS-триггер имеет три состояния, из которых два устойчивых (при снятии сигналов управления RS-триггер остаётся в установленном состоянии) и одно неустойчивое (при снятии сигналов управления RS-триггер не остаётся в установленном состоянии, а переходит в одно из двух устойчивых состояний).

RS-триггер используется для создания сигнала с положительным и отрицательным фронтами, отдельно управляемыми посредством стробов, разнесённых во времени. Также RS-триггеры часто используются для исключения так называемого явления дребезга контактов.

RS-триггеры иногда называют RS-фиксаторами[12].

-

Карта Карно асинхронного RS-триггера

-

Условное графическое обозначение асинхронного RS-триггера

-

Схема устранения дребезга контактов

-

Асинхронный RS-триггер с инверсными входами

RS-триггер синхронный

| C | S | R | Q(t) | Q(t+1) | Q(t+1) |

|---|---|---|---|---|---|

| 0 | x | x | 0 | 0 | 1 |

| 1 | 1 | 0 | |||

| 1 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 |

Схема синхронного RS-триггера совпадает со схемой одноступенчатого парафазного (двухфазного) D-триггера, но не наоборот, так как в парафазном (двухфазном) D-триггере не используются комбинации S=0, R=0 и S=1, R=1.

Алгоритм функционирования синхронного RS-триггера можно представить формулой

где x — неопределённое состояние.

-

Схема синхронного RS-триггера на элементах 2И-НЕ

-

Карта Карно синхронного RS-триггера

-

Условное графическое обозначение синхронного RS-триггера

RS-триггер синхронный двухступенчатый со сложной логикой

УГО этого триггера смотри на рис.1.

D-триггеры

D-триггеры также называют триггерами данных, так как на них строятся регистры данных. D-триггеры бывают одноступенчатые и двухступенчатые.

D-триггер синхронный

| D | Q(t) | Q(t+1) |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Синхронный парафазный D-триггер представляет собой объединение асинхронного RS-триггера и парафазного ключа на двух логических элементах 2И. В однофазном D-триггере добавляется один инвертор (НЕ) и входные данные со входа D поступают на инверсный вход D через инвертор.

D-триггер (D от англ. delay — задержка)[13][14][15] — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. После прихода активного фронта импульса синхронизации на вход С D-триггер открывается. Сохранение информации в D-триггерах происходит после спада импульса синхронизации С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой.

Рассуждая чисто теоретически, парафазный (двухфазный) D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы.

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине.

-

Условное графическое обозначение D-триггера

-

Пример D-триггера с дополнительными асинхронными инверсными входами S и R

В одноступенчатых D-триггерах во время прозрачности все изменения информации на входе D передаются на выход Q. Там, где это нежелательно, нужно применять двухступенчатые (двухтактные, Master-Slave, MS) D-триггеры.

D-триггер двухступенчатый

DV-триггер

V-вход полностью аналогичен С-входу, т.е. является вторым разрешающим запись входом.

Нехорошие D-триггеры

Со склада Wikimedia commons:

Этот одноступенчатый триггер при "1" на входе D при каждом тактовом импульсе производит короткий положительный импульс (риску), которой в хороших D-триггерах не должно быть.[16]

T-триггеры

Т-триггер часто называют счётным триггером, так как он является простейшим счётчиком до 2. Т-триггеры бывают только двухступенчатые.

Т-триггер асинхронный

Асинхронный Т-триггер не имеет входа разрешения переключения Т.

T-триггер синхронный

| T | Q(t) | Q(t+1) |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Синхронный Т-триггер[17][18], при единице на входе Т, по каждому такту на входе С изменяет своё логическое состояние на противоположное, и не изменяет выходное состояние при нуле на входе T. Т-триггер может строиться на JK-триггере, на двухступенчатом (Master-Slave, MS) D-триггере и на двух одноступенчатых D-триггерах и инверторе. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединяя входы J и К во вход Т. Наличие в двухступенчатом (Master-Slave, MS) D-триггере динамического входа С позволяет получить на его основе T-триггер. При этом инверсный выход Q соединяется со входом D, а на вход С подаются счётные импульсы. В результате триггер при каждом счётном импульсе запоминает значение , то есть будет переключаться в противоположное состояние.

Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена на 2.

TV-триггер

V-вход полностью аналогичен С-входу, т.е. является вторым разрешающим переключение входом.

Нехорошие Т-триггеры

Ряд нехороших Т-триггеров приведён на странице [1] в разделе "Нехорошие Т-триггеры".

JK-триггеры (универсальные триггеры)

JK-триггеры являются самыми сложными из двоичных триггеров. Так как JK-триггер может заменить RS-триггер, D-триггер и T-триггер, то его называют универсальным триггером.

JK-триггеры бывают только двухступенчатые со сложной логикой на входе триггера первой ступени.

| J | K | Q(t) | Q(t+1) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

JK-триггер[20][21] работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (от англ. Jump — прыжок) аналогичен входу S у RS-триггера. Вход K (от англ. Kill — убить) аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации.

На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К во вход Т[22].

Алгоритм функционирования JK-триггера можно представить формулой

-

Граф переходов JK-триггера

-

Карта Карно JK-триггера

-

Условное графическое обозначение JK-триггера

-

JK-триггер с дополнительными асинхронными инверсными входами S и R

Ложные "JK-триггеры"

Со склада Wikimedia commons:

![]()

В этих одноступенчатых триггерах при JK=11 реализуется устройство, которое при "0" на тактовом входе

устанавливается в "0", а при "1" на тактовом входе является генератором, т.е. не является Т-триггером, как это должно быть в обычных двухступенчатых (Master-Slave, MS) JK-триггерах.[23]

Триггеры с любым числом устойчивых состояний

Триггер с любым числом устойчивых состояний N строится из N логических элементов (N-1)ИЛИ-НЕ или (N-1)И-НЕ путём соединения выхода каждого элемента (Q0, Q1, …, Q(N-1)) с соответствующими входами всех других элементов[25]. То есть наименьшее число логических элементов для построения N-ичного триггера равно N.

Триггеры на элементах (N-1)ИЛИ-НЕ работают в прямом одноединичном коде (на выходе Q одного из элементов — «1», на выходах Q других элементов — «0»).

Триггеры на элементах (N-1)И-НЕ работают в инверсном однонулевом коде (на выходе Q одного из элементов — «0», на выходах Q других элементов — «1»).

При добавлении N транзисторов доступа эти триггеры могут работать как ячейки статической сверхоперативной памяти (SRAM).

При добавлении схем управления переключением эти триггеры могут работать как N-ичные аналоги двоичного RS-триггера.

В непозиционных системах счисления:

удельные затраты инверторов от числа состояний триггера не зависят: , где — число инверторов, — число состояний триггера.

Удельные затраты диодов в логических частях логических элементов от числа состояний триггера имеют линейную зависимость: , где x1 — число инверторов, x2 — число состояний триггера, (x2-1) — число диодов в логической части одного логического элемента. По этому параметру выгоднее двоичные триггеры.

В сдвоенных показательных позиционных системах счисления:

по теореме[источник не указан 4990 дней] Джона фон Неймана [26]

из целочисленных систем счисления наибольшим удельным числом представимых чисел и наименьшими аппаратными затратами обладают троичные триггеры, второе место занимают двоичные и четверичные триггеры.[источник не указан 4990 дней]

В приведённом выше подходе построения триггеров с любым числом устойчивых состояний при увеличении числа устойчивых состояний — n, увеличивается число входов в логических элементах в каждой элементарной ячейке триггера. Larry K. Baxter, Lexington, Mass. Assignee: Shintron Company, Inc., Cambridge, Mass. US Patent 3,764,919 Oct. 9, 1973 Filed: Dec. 22, 1972 Fig.3 предлагает другой подход к построению триггеров с любым числом устойчивых состояний, при котором число логических элементов и число входов в логических элементах в каждой элементарной ячейке триггера остаётся постоянным.

Физические реализации триггеров

Триггеры с тиристорами

Тиристор подходит для замены элемента памяти в триггерах.

Описание схемы на примере RS триггера: К катоду тиристора подключается выход триггера Q, к управляющему электроду подключается вход S, к аноду подключается постоянное напряжение через полевой транзистор с изолированным затвором, к затвору полевого транзистора подключается вход R.

Описание работы: Начальное состояние на выходе Q ноль: тиристор находится в замкнутом состоянии, ток на выходе соответствует нулю. Переход в состояние единица: на вход S подается напряжение равно логической единице тиристор разблокируется и напряжение на выходе Q повышается соответственно логической единице, при последующем понижении напряжения на входе S тиристор сохраняет низкое сопротивление и напряжение на выходе Q остается равным логической единице. Переход от логической единицы к нулю: на вход R подается напряжение равное логической единице полевой транзистор переходит в замкнутое состояние, напряжение на аноде тиристора падает, вследствии чего сопротивление тиристора возрастает и он переходит в состояние низкого выходного напряжения соответствующего логическому нулю, это состояние сохраняется при повышении входного напряжения на аноде тиристора.

Тиристор можно заменить на два биполярных транзистора (смотря какая реализация будет удобнее).

Как итог мы получаем RS триггер на трех транзисторах.

См. также

- Двоичная система счисления

- Бит

- Двоичные логические элементы

- Инвертор

- Троичный триггер

- Декатрон — ламповый счётчик с 10-ю устойчивыми состояниями.

- Счётчик (электроника)

- Регистр (цифровая техника)

- Компьютер

- Триггер Шмитта

Литература

- Зельдин Е.А. Триггеры. — Энергоатомиздат, 1983. — С. 96.

- Жан М. Рабаи, Ананта Чандракасан, Боривож Николич. Цифровые интегральные схемы. Методология проектирования = Digital Integrated Circuits. — 2-ое изд. — М.: «Вильямс», 2007. — С. 912. — ISBN 0-13-090996-3.

- Шамшин В. Г., История технических средств коммуникации. Учеб. пособие., 2003. Дальневосточный Государственный Технический Университет.

- Васюкевич В. О. Аналитика триггерных функций // Автоматика и вычислительная техника. — 2009. — № 4. — С. 21-29. — ISSN 0132-4160.

Примечания

- ↑ Страницы истории. 1918 год.

- ↑ William Henry Eccles and Frank Wilfred Jordan, «Improvements in ionic relays». British patent number: GB 148582 (filed: 21 June 1918; published: 5 August 1920).

- ↑ W. H. Eccles, F. W. Jordan A trigger relay utilizing three-electrode thermionic vacuum tubes. The Electrician, Vol. 83, P. 298 (19 September 1919). Перепечатано в Radio Review, Vol. 1, No. 3, P. 143—146 (December 1919)

- ↑ http://physicsbooks.narod.ru/Jansen/1.htm 4.40. Бистабильный мультивибратор (триггер)

- ↑ de.ifmo.ru — «Последовательностные Схемы»

- ↑ http://www.intuit.ru/department/hardware/archhard2/1/2.html Интернет университет. 1. Лекция: Основные функциональные элементы ЭВМ, часть 1. Триггер

- ↑ http://www.net-lib.info/11/4/536.php Константин Рыжов — 100 великих изобретений. 1919 г. — Триггер Бонч-Бруевича, Икклза и Джордана.

- ↑ http://potan.livejournal.com/91399.html Системы счисления (продолжение).

- ↑ Троичная цифровая техника; Перспектива и современность. 28.10.05 Александр Кушнеров, Университет им. Бен-Гуриона, Беэр-Шева, Израиль.

- ↑ http://dssp.karelia.ru/~ivash/ims/t10/TEMA4.HTM#DTRIGGER RS-триггер.

- ↑ http://it.fitib.altstu.ru/neud/shemotechnika/index.php?doc=teor&st=124 Схемотехника. ТЕМА 11. Триггерные схемы. Бистабильная ячейка. Схема устранения дребезга контактов. Асинхронные и синхронные триггеры. Однотактные и двухтактные триггеры. 11.1. Асинхронные RS-триггеры. 11.1.1. RS — триггер на двух элементах «2И-НЕ».

- ↑ http://masters.donntu.edu.ua/2001/fvti/tereschuk/diss/g2.htm 2 ЛОГИЧЕСКОЕ МОДЕЛИРОВАНИЕ СБИС НА ПЕРЕКЛЮЧАТЕЛЬНОМ УРОВНЕ. Рис.2.6-а) SR-фиксатор, б) Реализация SR-фиксатора на МОП-транзисторах

- ↑ http://dssp.karelia.ru/~ivash/ims/t10/TEMA4.HTM#DTRIGGER D-триггер.

- ↑ http://dfe3300.karelia.ru/koi/posob/log_basis/triger1.html Логические основы ЭВМ. D-Триггер

- ↑ http://cxem.net/beginner/beginner15.php Триггеры. Тактируемый D-триггер

- ↑ http://andserkul.narod2.ru/dvoichnie_d-triggeri/ Двоичные D-триггеры. Нехорошие D-триггеры

- ↑ http://digital.sibsutis.ru/digital/T_trigg.htm Т-триггеры.

- ↑ http://dssp.karelia.ru/~ivash/ims/t10/TEMA4.HTM#TTRIGGER Т-триггер

- ↑ http://andserkul.narod2.ru/dvoichnie_jk-triggeri/ Двоичные JK-триггеры

- ↑ http://dssp.karelia.ru/~ivash/ims/t10/TEMA4.HTM#DTRIGGER JK-триггер

- ↑ http://dfe3300.karelia.ru/koi/posob/log_basis/triger3.html Логические основы ЭВМ. JK-триггер

- ↑ www.gelezo.com — Триггеры

- ↑ Двоичные JK-триггеры. Нехорошие JK-триггеры

- ↑ http://sol.gfxile.net/atanua/ Сайт логического симулятора Atanua

- ↑ http://knol.google.com/k/%D0%B0%D0%BD%D0%B4%D1%80%D0%B5%D0%B9-%D0%BA%D1%83%D0%BB%D0%B8%D0%BA%D0%BE%D0%B2/%D0%B1%D0%B5%D1%81%D0%BA%D0%BE%D0%BD%D0%B5%D1%87%D0%BD%D1%8B%D0%B5-%D1%80%D1%8F%D0%B4%D1%8B-%D0%BE%D0%B4%D0%BD%D0%BE%D0%B5%D0%B4%D0%B8%D0%BD%D0%B8%D1%87%D0%BD%D1%8B%D1%85-%D0%B8/209nqpp00go3k/119# Бесконечные ряды одноединичных и однонулевых триггеров на элементах (n-1)ИЛИ-НЕ и (n-1)И-НЕ с любым числом устойчивых состояний с записью и чтением по выходным линиям Q0…Q(N-1)

- ↑ http://deepblue.lib.umich.edu/bitstream/2027.42/3972/5/bab6286.0001.001.pdf Раздел 5.2 Choice of binary system

Ссылки

- Лабораторная работа. Исследование триггеров

- Триггеры

- БСЭ. Статья «Триггер»

- 3. Триггеры

- D.1.1. Элементная база АЛУ. Триггер

- Схемотехника. ТЕМА 11. Триггерные схемы. Бистабильная ячейка. Схема устранения дребезга контактов. Асинхронные и синхронные триггеры. Однотактные и двухтактные триггеры.

- Прохоров А. М.,Алексеев Д. М. и др. Физическая энциклопедия, Большая Российская энциклопедия, 1998 г., 5 т. Стр.167. Триггер

- http://ivatv.narod.ru/zifrovaja_texnika/1_06.htm Изучение элементной базы цифровой техники. Иноземцев В. А. Глава 1. Раздел 6. Триггеры