POWER4: различия между версиями

Перейти к навигации

Перейти к поиску

| [отпатрулированная версия] | [отпатрулированная версия] |

Содержимое удалено Содержимое добавлено

Oleg4280 (обсуждение | вклад) Ссылки |

Oleg4280 (обсуждение | вклад) Ссылки |

||

| Строка 53: | Строка 53: | ||

* [https://www.ixbt.com/cpu/ibm-power4.shtml IBM POWER4 — процессор из параллельного мира]{{ref-ru}} |

* [https://www.ixbt.com/cpu/ibm-power4.shtml IBM POWER4 — процессор из параллельного мира]{{ref-ru}} |

||

* [https://www.ibm.com/ibm/history/ibm100/us/en/icons/power4/ IBM100 — Power 4 : The First Multi-Core, 1GHz Processor]{{ref-en}} |

* [https://www.ibm.com/ibm/history/ibm100/us/en/icons/power4/ IBM100 — Power 4 : The First Multi-Core, 1GHz Processor]{{ref-en}} |

||

* [https://www.osp.ru/os/2003/06/183106/ Power4: надежда мира RISC | Открытые системы. СУБД | Издательство «Открытые системы»]{{ref-ru}} |

|||

* [https://www.osp.ru/os/2004/01/183797/ Архитектура на базе POWER4 | Открытые системы. СУБД | Издательство «Открытые системы»]{{ref-ru}} |

|||

{{Архитектура POWER}} |

{{Архитектура POWER}} |

||

Версия от 18:44, 9 января 2019

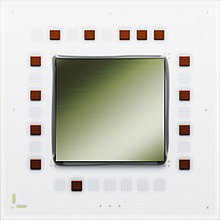

| POWER4 | |

|---|---|

| Центральный процессор | |

| |

| Производство | 2001 |

| Разработчик | IBM |

| Производитель | |

| Частота ЦП | 1.1—1.9 ГГц |

| Технология производства | 180—130 нм |

| Наборы инструкций | PowerPC |

| Число ядер | 2 |

| L1-кэш | 64 КБ + 32 КБ /ядро |

| L2-кэш | 1.41 МБ /чип |

| L3-кэш | 32 МБ /чип |

| Разъём | |

| Ядра | |

POWER4 — многоядерный микропроцессор компании IBM, выполняющий команды архитектуры PowerPC и являющийся продолжением серии POWER. Выпущен в 2001 г., содержит два ядра PowerPC.

Оба ядра 64-битные, основываются на архитектуре PowerPC AS, и используют общий кэш II уровня, который поделён на 3 части. Присутствует также контроллер кэша III уровня.

Суперскалярная архитектура позволяет процессору выполнять команды на 8 исполнительных устройствах одновременно.

Микропроцессор примечателен тем, что стал первым устройством, содержавшим два ядра на одной подложке. Более того, впервые были выпущены модули, содержавшие четыре микропроцессора.

См. также

Примечания

Ссылки

- IBM POWER4 — процессор из параллельного мира (рус.)

- IBM100 — Power 4 : The First Multi-Core, 1GHz Processor (англ.)

- Power4: надежда мира RISC | Открытые системы. СУБД | Издательство «Открытые системы» (рус.)

- Архитектура на базе POWER4 | Открытые системы. СУБД | Издательство «Открытые системы» (рус.)