Intersil/Harris 6100

| Intersil/Harris 6100 | |

|---|---|

| Центральный процессор | |

| |

| Производство | с 1976 по 1994 |

| Производители | |

| Частота ЦП | 3,3—8 МГц |

| Наборы инструкций | PDP-8 |

| Разъём | |

| Ядра | |

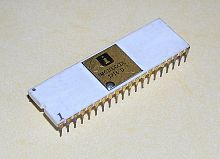

Intersil/Harris 6100 (IMS 6100) — 12-разрядный микропроцессор, совместимый по командам (с дополнительной TTL-обвязкой) с PDP-8/E. Также был известен под названием СMOS-8. Разработан в 1975 году[1][2]. Тактовая частота до 8 МГц, на кристалле размещено порядка 20 тысяч транзисторов.

Использовался в терминалах DEC VT78 (1978—1980 годы), рабочих станциях DECmate[англ.] (1980—1990 годы), компьютерах TLF MINI-12, Pacific CyberMetrix PCM-12, CESI SBC-8, ряде промышленных, военных и космических контроллеров. Кристаллы производились в «промышленном» и «военном» исполнении, в первом случае имея диапазон рабочих температур от −40 °C до +85 °C, во втором от −55 °C до +125 °C и повышенную устойчивость к радиации.

После прекращения производства в Intersil, небольшие партии клонов производила компания CESI, по крайней мере, до 1994 года. Отдельные системы на основе процессора находились в эксплуатации до 2000 года[3].

Архитектура

[править | править код]- Общий размер напрямую адресуемой памяти — 4096 12-битных слов. Код программ и данные хранятся совместно. Аппаратный стек в оригинальной версии отсутствует, в версии 6120 есть.

- Одно маскируемое прерывание.

- 64 порта ввода-вывода.

Регистры

[править | править код]- PC (Program Counter) — Программный счётчик (или указатель команды) — 12 бит.

- AC (Accumulator) — Аккумулятор — 12 бит.

- L (Linc) — Линк-регистр (или флаг) — 1 бит. Обычно эти два регистра при записи объединяли как AC/L

- MQ (Multiply Quotient) — 12 бит — вспомогательный, для временного хранения данных.

- MAR (Memory Addres Register) или OL (Output Latch) — 12 бит — регистр-указатель текущего адреса при обращениях к памяти и операциях ввода-вывода

В модификации 6120 были добавлены:

- SP1 и SP2 (Stack Pointers) — 12 бит — указатели стеков, доступные через регистр AC. Могли также использоваться как регистры для временного хранения данных. Для работы со стеком были введены инструкции PPCx, PACx, RTNx и POPx, где x — 1 или 2.

Имелись также служебные регистры:

- IR (Instruction Register) — 12 бит — Регистр инструкций, хранящий выполняемую команду.

- TEMP (Temporary Register) — регистр для временного хранения данных при исполнении инструкций процессором,

- Multiplexer — 12 бит — регистр — мультиплексор, содержал данные при передаче из/в процессор.

Для операций с памятью использовались регистры блока управления памятью: отдельного, в случае 6100, или интегрированного на кристалл для 6120.

- IF (Instruction Field) — 3 бита — Хранил три старших бита адреса, используемого для чтения инструкций, всех косвенных адресных указателей, и всех прямо адресуемых операндов. Мог быть прочитан в AC и загружен из IB,

- IB (Instruction Buffer) — 3 бита — Использовался в качестве буфера для инструкций, изменяющих IF. Мог быть загружен из битов инструкций, из AC и из ISF,

- ISF — 3 бита — сохранял содержимое IF при прерывании,

- DF (Data Field) — 3 бита — Хранил три старших бита адреса, используемого для всех косвенно адресуемых операндов,

- DSF (Data Save Field) — 3 бита — сохранял содержимое DF при прерывании.

Технические характеристики

[править | править код]- Тактовая частота (МГц): 3,3; 4 и 8, поздние версии стабильно разгонялись до 15

- Разрядность регистров: 12 бит

- Разрядность шины данных: 12 бит

- Разрядность шины адреса: 12 бит для 6100 и 15 бит для 6120; шина данных и шина адресов мультиплексирована.

- Объём адресуемой памяти: 4096 12-битных слов (6 8-битных килобайт)

- Напряжение питания: +5 В, +10 В для 8Мгц модели

- Технология производства: Silicon Gate CMOS

- Корпус: 40-контактный керамический или пластиковый DIP

Версии

[править | править код]С 1981 года выпускалась также модификация 6120, с интегрированным на кристалле менеджером памяти 6102 и некоторыми другими улучшениями. Чип 6102 добавлял ещё 3 линии к шине адреса, расширяя таким образом адресное пространство до 32К слов.

Модели

[править | править код]- Harris M3-6100-3

- Harris M3-6100-6

- Harris M3-6100-9

- Harris M3-6100C-5

- Intersil IM6100CPL

- Intersil IM6100IDL

- Intersil IM6100IPL

- Intersil IM6100AIDL

- Intersil IM6100AIPL

- Intersil IM6100AMDL

- Intersil IM6100CCDL

- Intersil IM6100CCPL

Специализированные микросхемы комплекта

[править | править код]- 6121 — контроллер прерываний

- 6101 — элемент параллельного интерфейса

- 6102 — менеджер памяти

- 6402/03 — микросхемы UART

Примечания

[править | править код]- ↑ The Explosion 1975-1976 » AntiqueTech. AntiqueTech.com (21 апреля 2009). Дата обращения: 19 июня 2017. Архивировано из оригинала 3 июля 2017 года.

- ↑ Bell, Gordon (1980), Family Tree of Digital's Computers, (Poster), Digital Equipment Corporation, Архивировано 3 октября 2020, Дата обращения: 19 июня 2017 Источник. Дата обращения: 19 июня 2017. Архивировано 3 октября 2020 года.

- ↑ Doug Jones's DEC PDP-8 FAQs. Дата обращения: 19 июня 2017. Архивировано 17 июня 2017 года.

Руководства

[править | править код]- «Intersil 6100 microprocessor architecture», CPU World (англ.)

- Intersil, «IM6100 CMOS Family Sampler» (англ.)

- «Intersil IM6100 CMOS 12 bit microprocessor», Bitsavers.org (англ.)

- «CMOS DIGITAL DATA BOOK. Part of the Harris Spectrum of Integrared Circuits. 12bit microprocessors and Peripherals», Bitsavers.org (англ.)