Кремний на изоляторе

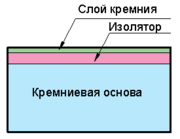

Кремний на изоляторе (КНИ, англ. Silicon on insulator, SOI) — технология изготовления полупроводниковых приборов, основанная на использовании трёхслойной подложки со структурой кремний-диэлектрик-кремний вместо обычно применяемых монолитных кремниевых пластин. Кроме собственно наименования технологии, термин «кремний на изоляторе» также часто употребляется в качестве названия поверхностного слоя кремния в КНИ-структуре.

Конструктивное исполнение

[править | править код]

а) Классической

б) КНИ

Подложка, выполненная по технологии кремний на изоляторе, представляет собой трёхслойный пакет, который состоит из монолитной кремниевой пластины, диэлектрика и размещённого на нём тонкого поверхностного слоя кремния. В качестве диэлектрика может выступать диоксид кремния SiO2 или, гораздо реже, сапфир (в этом случае технология называется «кремний на сапфире» или КНС)[1]. Дальнейшее производство полупроводниковых приборов с использованием полученной подложки по своей сути практически ничем не отличается от классической технологии, где в качестве подложки используется монолитная кремниевая пластина.

В первую очередь технология КНИ находит применение в цифровых интегральных схемах (в частности, в микропроцессорах), большая часть которых в настоящее время выполняется с использованием КМОП (комплементарной логики на МОП-транзисторах). При построении схемы по данной технологии большая часть потребляемой мощности затрачивается на заряд паразитной ёмкости изолирующего перехода в момент переключения транзистора из одного состояния в другое, а время, за которое происходит этот заряд, определяет общее быстродействие схемы. Основное преимущество технологии КНИ состоит в том, что за счёт тонкости поверхностного слоя и изоляции транзистора от кремниевого основания удаётся многократно снизить паразитную ёмкость, а значит и снизить время её зарядки вкупе с потребляемой мощностью. Данная технология позволяет добиться существенного повышения быстродействия микроэлектронных схем при одновременном снижении потребляемой мощности и габаритных размеров[2]. Так, например, максимальная частота переключения транзисторов (Ft), выполненных по технологическому процессу 130 нм, может достигать 200 ГГц[3][4]; в перспективе, при переходе к технологическим процессам с меньшим размером активных элементов[5] (уже существующему 22 нм, или только разрабатываемому сейчас[когда?] 10 нм), возможно ещё большее повышение этого показателя.

Другое преимущество технологии КНИ — превосходная стойкость к ионизирующим излучениям (радиационная стойкость), поэтому такая технология широко используется для аэрокосмического и военного электронного оборудования.

Недостаток технологии КНИ — большая стоимость.

Технология изготовления

[править | править код]В настоящее время наиболее распространены КНИ-подложки, где в качестве изолятора выступает диоксид кремния. Такие подложки могут быть получены различными способами, основные из которых: ионная имплантация, сращивание пластин[англ.], управляемый скол[англ.] и эпитаксия[6].

Ионная имплантация

[править | править код]Технология ионной имплантации также известна как ионное внедрение, имплантация кислорода, ионный синтез захороненных диэлектрических слоев и SIMOX (англ. Separation by IMplantation of OXygen). При использовании данной технологии монолитная кремниевая пластина подвергается интенсивному насыщению кислородом путём бомбардировки поверхности пластины его ионами с последующим отжигом при высокой температуре, в результате чего образуется тонкий поверхностный слой кремния на слое оксида. Глубина проникновения ионов примеси зависит от уровня их энергии, а поскольку технология КНИ подразумевает достаточно большую толщину изолирующего слоя, то при производстве подложек приходится использовать сложные сильноточные ускорители ионов кислорода. Это обусловливает высокую цену подложек, изготовленных по этой технологии, а большая плотность дефектов в рабочих слоях является серьёзным препятствием при массовом производстве полупроводниковых приборов.

Сращивание пластин

[править | править код]При использовании технологии сращивания пластин[англ.] (англ. wafer bonding) образование поверхностного слоя производится путём прямого сращивания второй кремниевой пластины со слоем диоксида. Для этого гладкие, очищенные и активированные за счёт химической или плазменной обработки пластины подвергают сжатию и отжигу, в результате чего на границе пластин происходят химические реакции, обеспечивающие их соединение[7]. Данная технология практически идеальна для изготовления КНИ-подложек с толстым поверхностным слоем, но с уменьшением его толщины начинает нарастать плотность дефектов в рабочем слое, а кроме того, усложняется технологический процесс и, как следствие, растёт стоимость готовых изделий. В результате, подложки с толщиной поверхностного слоя менее одного микрометра, которые наиболее востребованы при производстве быстродействующих схем с высокой степенью интеграции, имеют тот же набор недостатков, что и подложки, изготовленные по технологии ионной имплантации[6].

Управляемый скол

[править | править код]

Технология управляемого скола[англ.] (англ. Smart Cut), разработанная французской компанией Soitec[англ.], объединяет в себе черты технологий ионного внедрения и сращивания пластин[8]. В данном технологическом процессе используются две монолитные кремниевые пластины. Первая пластина подвергается термическому окислению, в результате чего на её поверхности образуется слой диоксида, затем верхняя лицевая поверхность подвергается насыщению ионами водорода с использованием технологии ионного внедрения. За счёт этого в пластине создаётся область скола, по границе которой пройдёт отделение оставшейся массы кремния. По завершении процедуры ионного внедрения пластина переворачивается и накладывается лицевой стороной на вторую пластину, после чего происходит их сращивание. На завершающей стадии проводится отделение первой пластины, в результате которого на поверхности второй остаётся слой диоксида и тонкий поверхностный слой кремния. Отделённая часть первой пластины используется в новом производственном цикле.

Производство КНИ-подложек по технологии управляемого скола требует большого количества операций, но в его процессе используется только стандартное оборудование. Кроме того, важным достоинством пластин, полученных по этой технологии, является низкая плотность дефектов в рабочем слое.

Эпитаксия

[править | править код]В случае использования эпитаксиальной технологии (англ. seed method) поверхностный слой образуется за счёт выращивания кремниевой плёнки на поверхности диэлектрика. Активные элементы, полученные на таких подложках, демонстрируют отличные рабочие характеристики, но большое число технологических проблем, связанных с эпитаксиальным процессом, пока ещё[когда?] не дают возможностей для массового внедрения этой технологии.

Использование в технике

[править | править код]Информация в этой статье или некоторых её разделах устарела. |

Перечень ряда устройств, произведённых с использованием КНИ-подложек, приведён ниже.

- Opteron (основанные на архитектуре k8) — семейство процессоров компании AMD, выпускаемых по технологическим процессам 130 нм (одноядерные) и 90 нм (одно- и двухъядерные)

- Cell — восьмиядерный процессор, совместно разработанный компаниями Sony, Toshiba и IBM (технологический процесс — 90 нм), используется в игровой приставке Sony PlayStation 3

- Xenon — трёхъядерный процессор компании IBM (технологический процесс — 90 нм, 65 нм), используется в игровой приставке Microsoft Xbox 360

- Broadway — процессор компании IBM (технологический процесс — 90 нм), используется в игровой приставке Nintendo Wii

Девятое поколение процессоров Intel Core 2, выполненных по технологическому процессу 65 нм, напротив, производится на основе обычных монолитных кремниевых пластин.

См. также

[править | править код]- Кремниевая пластина

- Напряжённый кремний[англ.]

- Планарная технология

- Пористый кремний

- Фотолитография

- Intel TeraHertz

Ссылки

[править | править код]- SOI Technology: IBM’s Next Advance In Chip Design — обзорная статья о КНИ и общих принципах функционирования современных цифровых микросхем

- AMDboard — большая подборка ссылок на публикации, посвященные КНИ /вебархив/

Примечания

[править | править код]- ↑ В старинном компьютере HP обнаружен загадочный прозрачный процессор Архивная копия от 1 января 2024 на Wayback Machine ... В винтажном компьютере Hewlett-Packard 1977 года компьютере найдена прозрачная микросхема Архивная копия от 1 января 2024 на Wayback Machine // 22 декабря 2023

- ↑ SOI technology for the GHz era. Дата обращения: 28 января 2007. Архивировано из оригинала 25 апреля 2006 года.

- ↑ http://www-03.ibm.com/press/us/en/pressrelease/7819.wss Архивная копия от 14 февраля 2011 на Wayback Machine IBM Announces Next Generation Silicon Germanium Technology. Cost Effective, Power Efficient Technology Drives Innovative New Wireless Applications and Devices] // IBM, 05 Aug 2005: «Advanced SiGe NPNs, Emitter width= 120nm, Ft = 200 GHz (8HP), Ft=100 GHz (8WL)»

- ↑ Архивированная копия. Дата обращения: 15 мая 2015. Архивировано из оригинала 6 марта 2016 года.

- ↑ Хотя технология КНИ может быть использована для построения любых полупроводниковых приборов, чаще всего речь идёт о МОП-транзисторах, характерным размером которых является длина канала, и именно эта величина указывается в наименовании технологического процесса

- ↑ 1 2 Исследование структур типа «кремний на пористом кремнии» и создание технологического процесса для производства приборов на их основе. Дата обращения: 28 января 2007. Архивировано 13 июня 2008 года.

- ↑ Инфракрасная спектроскопия кремниевых сращённых пластин. Дата обращения: 28 января 2007. Архивировано 28 сентября 2007 года.

- ↑ Smart Cut A guide to the technology, the process, the products. Дата обращения: 28 января 2007. Архивировано из оригинала 14 октября 2007 года.