Active-HDL

Текущая версия страницы пока не проверялась опытными участниками и может значительно отличаться от версии, проверенной 23 августа 2014 года; проверки требуют 6 правок.

| Active-HDL | |

|---|---|

| | |

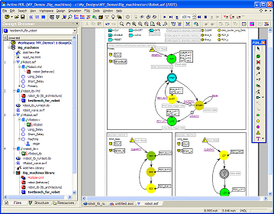

Программа Active-HDL 8.2 | |

| Тип | Проектирование FPGA |

| Разработчик | Aldec |

| Операционная система | Microsoft Windows |

| Языки интерфейса | английский язык |

| Первый выпуск | 1997 |

| Последняя версия | 8.3 (2010) |

| Лицензия | Коммерческое приложение |

| Сайт | aldec.com/activehdl/ |

Active-HDL — среда разработки, моделирования и верификации проектов для программируемых логических интегральных схем, разработанная фирмой Aldec. Первая версия программы вышла в 1997 году[1] .

Программа позволяет вводить устройства с помощью языков описания аппаратуры, а также с помощью структурных схем. Изначально программа поддерживала только язык VHDL, но со временем добавилась поддержка языков Verilog и SystemC[2]. С помощью программы можно графически проектировать конечные автоматы[3], а также конвертировать HDL описание в графические структурные схемы и обратно.

Программа снабжена мощным ядром моделирования. Поддерживается совместная работа с программами MatLab и Simulink[4].

Примечания

[править | править код]- ↑ Aldec Company timeline

- ↑ FPGA World Aldec releases Active-HDL 6.3 with integrated SystemC Архивная копия от 18 августа 2010 на Wayback Machine

- ↑ Aldec.com State Machine Editor Overview Архивная копия от 14 июня 2010 на Wayback Machine Архивировано 14 июня 2010 года.

- ↑ EMA Design Solutions Aldec Active HDL Архивная копия от 6 января 2011 на Wayback Machine Архивировано 6 января 2011 года.

Ссылки

[править | править код]Aldec Active HDL 8.2 User Manual (недоступная ссылка)